Redundant Binary (RB) System

The redundant binary (RB) number system was invented by Avizienis in 1961 in order to implement the parallel adder which has no carry-propagation in the critical path of the adder. Redundant binary number is sometimes called as binary signed numbers because the digit set of this system has 3 symbols, {1, 0, -1}. The below figure shows how the redundant binary addition can be done without carry-propagation.

Nowadays, many VLSI researchers have tried to implement multipliers, dividers to reduce the delay time with the help of the carry-free addition. Also they are dealing with other complicated arithmetic units such as modular multipliers and FIR filters using RB number system, because these operations consist of the iterative and successive additions and subtractions. However, the RB number system has a disadvantage of an overhead of RB-NB conversion time. Therefore, the design issue of the RB number system is to minimize the overhead of RB-NB conversion and to increase the overall performance, compared to the normal binary number system.

New Adder Design with the Reduced P, G Signal Generations

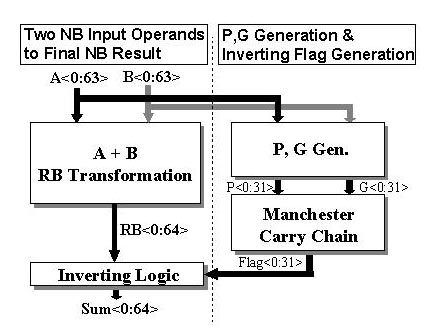

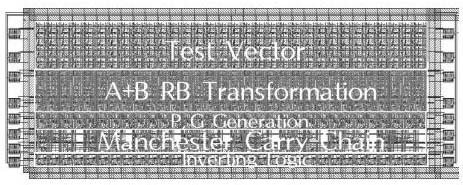

The motivation of this adder is to reduce the P, G signal generations so as to minimize the overall delay time of the adder. The principles of reducing the P, G signal generations is as below:

The overhead of RB-NB conversion can be reduced if the RB number has a small amount of '-1' symbols. '-1' symbol causes the carry-propagation while converting RB to NB. In order to acquire the high performance, the new adder scheme adapts the internal use of the RB number system, which has a small amount of '-1' symbols. Then, the frequency of the P, G signal generations can be diminished because '-1' symbol can be used for the G signal and '0' symbol for the P signal. With this new P, G generation scheme, the frequency of the internal carry generation can be reduced. This fact implies the average delay time and the power consumption can be reduced.

The below figures show the structure and the layout of the new adder.

The below figures show the structure and the layout of the new adder.

The SPICE simulation result of this adder shows that the worst case delay time is 0.6ns under 2.5 V and 85 degree temperature with 0.25um 5-metal CMOS process, and 15% of the average delay time reduction can be acquired.

FIR Filter Design using Redundant Binary Number System

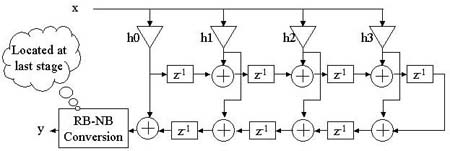

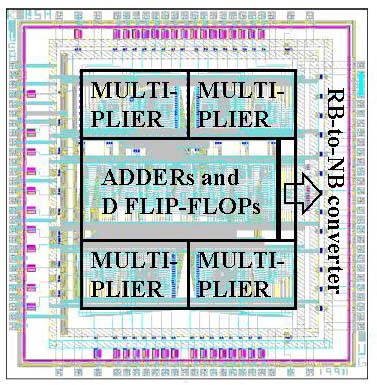

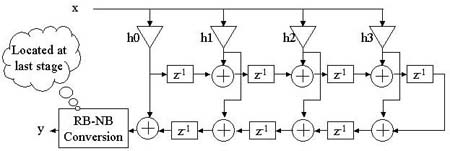

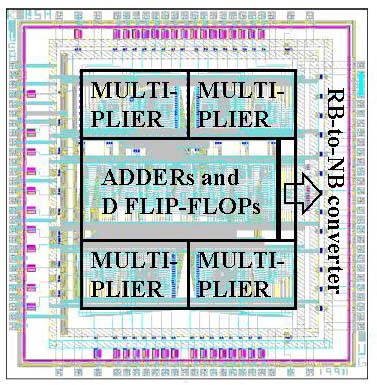

A high performance FIR filter using RB number system is designed. In the past, FIR filter were implemented by NB number system; therefore, the speed was limited due to the carry propagation. We realized a fast FIR filter by utilizing the carry-free property of RB system. A RB partial product generator circuit is devised without Booth's algorithm, so that the delay and complexity of the filter is reduced. The serious demerit of RB system, RB-NB conversion delay, is effectively overcome by utilizing pipeline architecture. The below figures show the pipeline structure and the layout of the FIR filter.

The chip is fabricated by using 0.65 um 2-metal CMOS process. The active area size is 2.6mm x 2.6mm and the number of the transistor is 27,000. The operating frequency is 230 MHz under the condition of 5V supply voltage.

The Floating-Point Datapath System using RB Number

We are now developing the FP datapath system. Many FP datapath systems using RB number has been reported but all systems are developed with the restricted use of RB number system. Only the components like adder and multiplier are internally designed with RB number system and the produced output result is NB number, which is converted from RB number.

In this design, we want to use RB number to the whole FP datapath system so that the internal FP datapath can be designed with carry-free operations without RB-NB conversion and the RB-NB conversion is performed only at the I/O part of the datapath. High performance due to the whole use of RB number system is expected compared to the current FP datapath system.

In this design, we want to use RB number to the whole FP datapath system so that the internal FP datapath can be designed with carry-free operations without RB-NB conversion and the RB-NB conversion is performed only at the I/O part of the datapath. High performance due to the whole use of RB number system is expected compared to the current FP datapath system.

Related Publications

- Kyung-Nam Han, Sang-Wook Han, Euisik Yoon, "A New Adder Scheme with Reduced P, G Signal Generations using Redundant Binary Number System", ISCAS 2000, (printing)

- Sung-Ho Baik, Kyung-Nam Han, Euisik Yoon, "A 230MHz 8 tap Programmable FIR filter Using Redundant Binary Number System", Proceedings of ISCAS '99, pp 415-418, 1999.