Information

Capacitive-type CMOS fingerprint sensors are considered as one of the attractive solutions for user authentication systems especially for mobile equipment. However, they are susceptible to image degradation; therefore, the captured fingerprints require complicated image processing algorithms for fingerprint identification. For fingerprint image enhancement, capacitive diffusion networks are developed to generate a local threshold level. To achieve an inexpensive fingerprint identification system in a compact size, single-chip fingerprint sensors with pixel-level processors that perform 1b morphological operations have been reported. Because these sensors contain the dedicated simple pixel-parallel processors, they cannot perform advanced image processing algorithms required for most fingerprint identification systems.

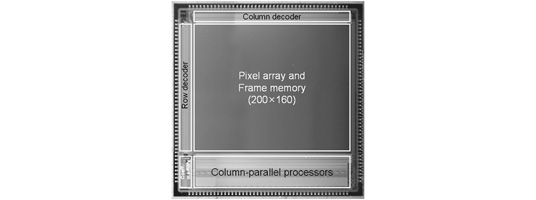

We have proposed a CMOS fingerprint recognition SoC with a new pixel architecture and embedded column-parallel processors optimized for 2-D digital image processing. The proposed sensor employs self-configuration column-parallel processors for adaptive filter operations and performs various image processing algorithms. The proposed pixel includes a sensing block, ADC and frame memory with no area penalty.

We have proposed a CMOS fingerprint recognition SoC with a new pixel architecture and embedded column-parallel processors optimized for 2-D digital image processing. The proposed sensor employs self-configuration column-parallel processors for adaptive filter operations and performs various image processing algorithms. The proposed pixel includes a sensing block, ADC and frame memory with no area penalty.

Figures

Figure 1. Chip Micrograph

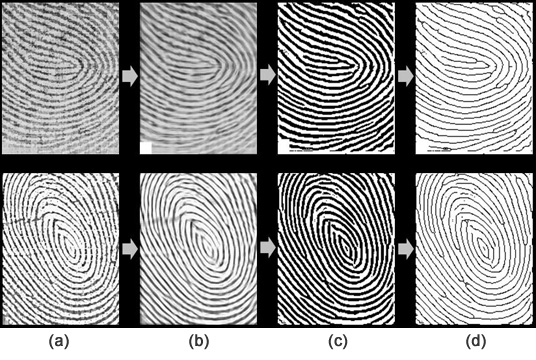

Figure 2. Sample images from the fabricated chip. (a) captured raw image, (b) processed image after smoothing, (c) processed image after directional band pass filtering and binarization, and (d) processed image after thinning.

Related Publications

- Seong-Jin Kim, Kwang-Hyun Lee, Sang-Wook Han, Euisik Yoon, A 200x160 Pixel CMOS Fingerprint Recognition SoC with Adaptable Column-Parallel Processors, Technical Digest of International Solid-State Circuits Conference, pp.250-251. Feb. 2005.