#### UNIVERSITY OF MINNESOTA

UNITE

- Class will be broadcast through the UNITE system

- Streaming video available

#### - www.myu.umn.edu

- Please attend class for more interaction

- To encourage your attendance, video will be available 10 days after the actual lecture (standard UNITE policy – no exceptions)

#### UNIVERSITY OF MINNESOTA

# **Class Material**

• Textbook:

"Digital Integrated Circuits – A Design Perspective",

2<sup>nd</sup> ed, by J. Rabaey, A. Chandrakasan, B. Nikolic

- Writing on the board versus powerpoint

- Other references

- I. E. Sutherland, R. F. Sproull, and D. F. Harris, Logical effort : Designing fast CMOS circuits, Morgan Kaufmann, San Francisco, CA, 1999.

- Y. Taur, T. Ning, Fundamentals of Modern VLSI Devices, Cambridge University Press, 2002.

## UNIVERSITY OF MINNESOTA

# **Academic Integrity**

- Students caught engaging in an academically dishonest practice will receive a failing grade for the course.

- University policy on academic dishonesty will be followed strictly.

- -http://www1.umn.edu/oscai/

#### UNIVERSITY OF MINNESOTA

### **Policies**

- Homework must be received before class

- 3 days of grace period to be used for all assignments (e.g., 1 day each for 3 assignments, or 3 days on one assignment)

- After the grace period is used up, late submission results in a zero grade

- Zero tolerance for cheating

- Collaboration OK, copying NOT OK

- No extra work for extra credit

- Check class web pages regularly. Students are responsible for checking their email, the discussion threads and the announcements section on class web page regularly

### University of Minnesota Grading Policy

- 20% Homework and quizzes

- 20% final project

- Two phases

- Requires a lot of time

- 25% Midterm open notes, open book.

- 35% Final exam open notes, open book

#### UNIVERSITY OF MINNESOTA

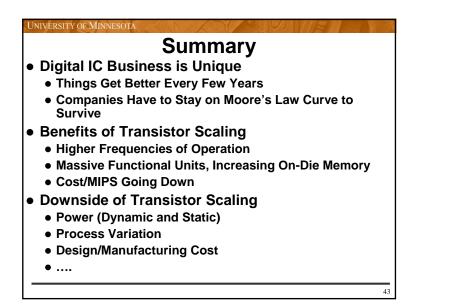

### **Course Overview**

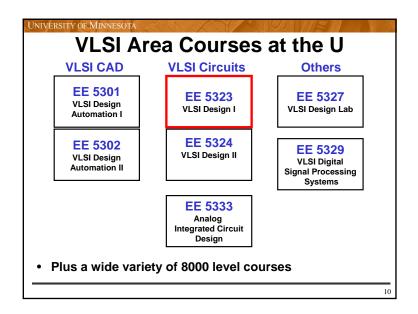

- This class is intended to be an introduction to the design of very large scale integrated (VLSI) circuits. It is the first part of a two-semester sequence: this part focuses on the transistor-level and logic-level aspects, while the second part, EE 5324, concentrates on designing circuits that implement various functionalities (e.g. memories, datapath units).

- The main objective of the two-semester sequence is to provide the student with the capability of designing digital VLSI circuits.

11

| Processors       |

|------------------|

| 0.6μ 0.35μ 0.25μ |

|                  |

|                  |

|                  |

| L.com/           |

|                  |

| Year                       | 2001 | 2003 | 2005 | 2007 | 2010      | 2013 | 2016  |

|----------------------------|------|------|------|------|-----------|------|-------|

| DRAM ½ pitch [nm]          | 130  | 100  | 80   | 65   | I 1 E     | 32   | 22    |

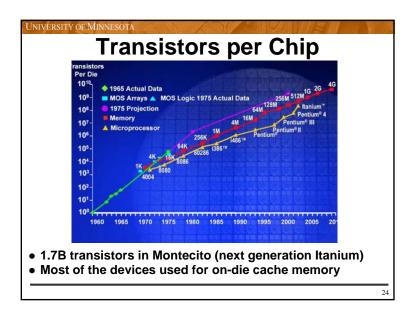

| MPU transistors/chip       | 97M  | 153M | 243M | 386M | · · · · · |      | 3.09G |

| Wiring levels              | 8    | 8    | 10   | 10   | 10        | 11   | 11    |

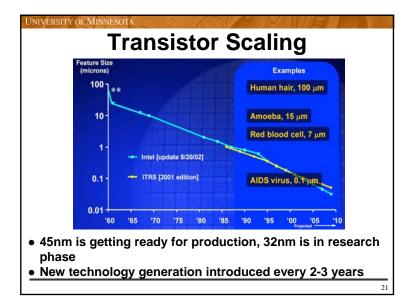

| High-perf. phys. gate [nm] | 65   | 45   | 32   | 25   | 1         |      | - 9   |

| High-perf. VDD [V]         | 1.2  | 1.0  | 0.9  | 07   | L .       | 5    | 0.4   |

| Local clock [GHz]          | 1.7  | 3.1  | 5.2  | -6.7 | 2 (       | Hz   | 28.8  |

| High-perf. power [W]       | 130  | 150  | 170  | 190  | 218       | 251  | 288   |

| Low-power phys. gate [nm]  | 90   | 65   | 45   | 32   | 22        | 16   | 11    |

| Low-power VDD [V]          | 1.2  | 1.1  | 1.0  | 0.9  | 0.8       | 0.7  | 0.6   |

| Low-power power [W]        | 2.4  | 2.8  | 3.2  | 3.5  | 3.0       | 3.0  | 3.0   |