# --- University of Minnesota ---

Institute of Technology

Department of Electrical Engineering

# Midterm#2 Open book, open notes, take home To be handed out November 20, 1998 To be returned November 23, 1998 (before start of class)

# **EE5505: Analog Integrated Circuit Design**

**Fall 1998**

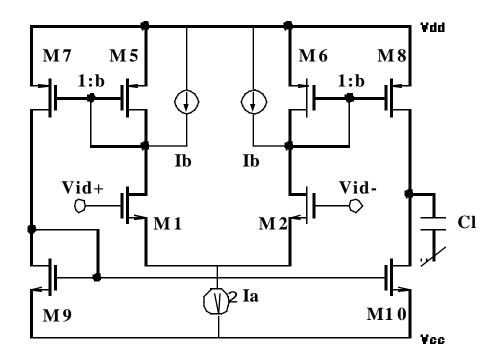

1) This is a design problem. However before completing the design we are required to complete the analysis. For each question show your work and also put down the device numbers associated with each circuit parameter. For example when referring to the transconductance of M5 refer to it as gm5. The bottom current mirror (M9 and M10) have a gain of 1. Let  $L_0 = 1.2 \mu M$  (minimum process length). Let lambda $_0 = 0.03$ . Let  $W_0 = 1.8 \mu M$  (minimum process width). Let tox=300A°. Let Kn=46e-6, Let Kp=19e-6. Let KFp=5e-25 and KFn=1.2e-23. (KFp and KFn are the ones used in HSPICE)

- a) For the circuit on the previous page derive an expression for the small-signal low frequency gain in terms of transconductances and output conductances. (5points)

- b) Next develop the same expression in terms of device geometries and bias currents (2points)

- c) Find an expression for the unity gain frequency of this circuit. (5points)

- d) Find an expression for the slew-rate of the amplifier (5points)

- e) Find an expression for the input common-mode range in terms of delta\_vgs and threshold voltages. (5points)

- f) Find an expression for the output common-mode range in terms of delta\_vgs and threshold voltages. (5points)

- g) Find and expression for the input referred noise of this circuit. Let the noise for the bais current network be equal to Ia<sup>2</sup> and Ib<sup>2</sup> respectively. (5 points)

- h) Find an expression for the non-dominant pole in this circuit in terms of device capacitances, transconductances and output conductances (5 points)

- i) For Ib=0.5\*Ia design a circuit that has the following characteristics. Design a circuit that gives you the minimim power and area. Show all steps for each characteristics. Give all device geometries. Set b=3. (50 points)

Cl=10pF Slew-Rate= 5V/µS Vdd=5.0 Vss=0.0 UGF=1.2MHz Gain (low frequency)≥60dB Vomax=4.5V, Vomin=0.5V Vinmin=1.0, (let delta\_vgs of Ia=0.3V) Vinmax=4.0, (let delta\_vgs of Ib=0.3V) Input referred noise from 0.1Hz to 1kHz ≤ 15µV.

j) EXTRA CREDIT (confirm your results with SPICE (Use the model parameters and the end of the paper. These are the same as those on my web-site.)] (10 points)

2) For this question use the parameters given below. Design a CMOS current mirror that meets the following set of specifications. Assume that the input and output nodes, shown in the figure below, are connected to ideal current sources with no capacitive or resistive components. Also assume that the common source terminal is connected to the ground node. Neglect thermal noise and drain-to-bulk capacitance. Select the appropriate current mirror topology and calculate the required device sizes. [15 points]

$$\begin{array}{ll} \text{small-signal output resistance } r_{O} & \geq 10 \text{ Meg } \Omega \\ \text{minimum output voltage range } V_{Omin} & = 0.5 \text{ V} \\ \text{output flicker noise current @ 100Hz} & \leq 75.6 \text{pA}/\sqrt{\text{Hz}} \\ \text{output pole frequency (3dB freq)} & \geq 50 \text{ MHz} \\ \text{quiescent current } I_{in} & = 20 \mu \text{A} \end{array}$$

$$\begin{array}{l} \lambda_{min}*L_{min} \\ \lambda = \frac{\lambda_{min}*L_{min}}{L} & \text{where } L_{min} \text{ is the process minimum length.} \\ \lambda_{min} = 0.2 \\ k'_{nmos} = 40E-6 \\ k'_{nmos} = 15E-6 \\ L_{min} = 4\mu m \\ W_{min} = 4\mu m \\ Cgd = CGD0*W \\ CGDO = 3E-10 \\ \epsilon_{ox} = 3.5E-11 \text{ Farads/Meter} \\ T_{ox} = 400A^{\circ} \\ Cgs = \frac{2}{3} \left(L^*W^*C_{ox}\right) \\ \hline e_{eq}^2 \left(\text{flicker}\right) = \frac{KF}{2*f^*C_{ox}*W^*L^*k'} & \text{gate referred flicker noise voltage} \\ \end{array}$$

KF = 2.5E-27

## SPICE MODEL to be used for simulation purposes

#### \*N86O SPICE LEVEL3 PARAMETERS

\* Copied from MOSIS website 9/22/98 (models extracted Aug 98)

### .MODEL CMOSN NMOS LEVEL=3 PHI=0.700000 TOX=3.1600E-08 XJ=0.200000U TPG=1

- + VTO=0.6488 DELTA=1.3120E+00 LD=1.1000E-09 KP=7.4931E-05

- + UO=685.7 THETA=1.0510E-01 RSH=1.4430E+01 GAMMA=0.6375

- + NSUB=1.4620E+16 NFS=7.1250E+11 VMAX=1.9690E+05 ETA=8.7220E-02

- + KAPPA=1.7070E-01 CGDO=5.0000E-11 CGSO=5.0000E-11

- + CGBO=3.3679E-10 CJ=2.8467E-04 MJ=5.1265E-01 CJSW=1.2852E-10

- + MJSW=1.0000E-01 PB=9.6031E-01

- \* Weff = Wdrawn Delta\_W

- \* The suggested Delta\_W is 8.8200E-07

### .MODEL CMOSP PMOS LEVEL=3 PHI=0.700000 TOX=3.1600E-08 XJ=0.200000U TPG=-1

- + VTO=-0.7917 DELTA=2.6770E+00 LD=9.1170E-10 KP=1.9473E-05

- + UO=178.2 THETA=1.0930E-01 RSH=1.2190E+00 GAMMA=0.3303

- + NSUB=3.9240E+15 NFS=6.4990E+11 VMAX=1.8190E+05 ETA=1.3250E-01

- + KAPPA=9.0000E+00 CGDO=5.0000E-11 CGSO=5.0000E-11

- + CGBO=3.2839E-10 CJ=2.8734E-04 MJ=4.3663E-01 CJSW=1.6570E-10

- + MJSW=1.0000E-01 PB=7.6293E-01

- \* Weff = Wdrawn Delta\_W

- \* The suggested Delta\_W is 8.4240E-07